Roblex Nana Mines Paris - PSL, Centre de Recherche en Informatique (CRI) Fontainebleau, France roblex.nana\_tchakoute@minesparis.psl.eu

Petr Dokladal

Mines Paris - PSL, Centre de Morphologie Mathématique (CMM) Fontainebeau, France petr.dokladal@minesparis.psl.eu

### ABSTRACT

For various reasons including those related to climate changes, energy has become a critical concern in all relevant activities and technical designs. For the specific case of computer activities, the problem is exacerbated with the emergence and pervasiveness of the so called *intelligent devices*. From the application side, we point out the special topic of Artificial Intelligence, who clearly needs an efficient computing support in order to succeed in its purpose of being an ubiquitous assistant. There are mainly two contexts where energy is one of the top priority concerns: embedded computing and supercomputing. For the former, power consumption is critical because the amount of energy that is available for the devices is limited. For the latter, the heat dissipated is a serious source of failure and the financial cost related to energy is likely to be a significant part of the maintenance budget. On a single computer, the problem is commonly considered through the electrical power consumption. This paper, written in the form of a survey, we depict the landscape of energy concerns in computer activities, both from the hardware and the software standpoints.

# **KEYWORDS**

Energy profiling, power measurement, HPC systems, Embedded systems, Optimization

Contents

| Abstr | ract                                             | 1  |

|-------|--------------------------------------------------|----|

| Conte | ents                                             | 1  |

| 1     | Introduction                                     | 1  |

| 2     | Related Review Works                             | 2  |

| 3     | Overview of energy metrics in HPC                | 3  |

| 3.1   | Standard energy consumption metrics              | 3  |

| 3.2   | Energy metrics in supercomputers                 | 3  |

| 3.3   | From energy to Carbon footprint                  | 4  |

| 4     | Hardware architecture from the energy standpoint | 5  |

| 4.1   | Accelerators                                     | 5  |

| 4.2   | Embedded systems: Microcontrollers               | 5  |

| 4.3   | General Purpose Processors                       | 6  |

| 5     | Energy management tools                          | 7  |

| 5.1   | Energy tools for GPUs                            | 7  |

| 5.2   | Energy tools for CPUs                            | 7  |

| 5.3   | Energy tools for microcontrollers                | 8  |

| 5.4   | Energy tools for Modern HPC systems              | 8  |

| 6     | About cooling Systems                            | 11 |

| 6.1   | Cooling technologies for HPC systems             | 11 |

Claude Tadonki Mines Paris - PSL, Centre de Recherche en Informatique (CRI) Fontainebleau, France claude.tadonki@minesparis.psl.eu

# Youssef Mesri

Mines Paris - PSL, Centre de Mise en Forme de Matériaux (CEMEF) Sophia Antipolis, France youssef.mesri@minesparis.psl.eu

| 6.2   | News trends in liquid cooling design        | 12 |

|-------|---------------------------------------------|----|

| 7     | Energy Optimization techniques              | 12 |

| 7.1   | Static energy optimization approaches       | 12 |

| 7.2   | Dynamic energy optimization approaches      | 14 |

| 7.3   | Hybrid energy optimization approaches       | 14 |

| 8     | Energy of AI processing                     | 14 |

| 8.1   | Motivation                                  | 14 |

| 8.2   | Studies on CO <sub>2</sub> concerns with AI | 15 |

| 8.3   | Energy profiling tools for AI applications  | 15 |

| 8.4   | Energy optimization of AI applications      | 16 |

| 9     | Prospective viewpoint                       | 17 |

| 10    | Conclusion                                  | 17 |

| Refer | ences                                       | 18 |

|       |                                             |    |

# **1** INTRODUCTION

Manufacturers of high performance computing (HPC) systems are striving to provide more and more potential computing power by acting on the related hardware aspects like: *number of cores*, *vectors units*, *3-operands units*, *accelerators*, to name the main ones. Performance is a high priority in servers and supercomputers beside storage capacity. In order to leverage the potential power of HPC systems, efforts are made reach better implementations through cutting-edge programming and code optimisation techniques [126]. The reality is that these performance-guided activities do not explicitly consider the energy efficiency. Energy saving has become one of the main challenges for the new generations of servers and supercomputers.

Nowadays, the design of HPC systems considers *power efficiency*: 21.1 MW for the 1.102 EFlop/s FRONTIER, 29.9 MW for the 442 PFlop/s FUGAKU, and 2.94 MW for the 151.9 PFlop/s LUMI to consider the top 3 machines of the most recent TOP500 list [37]. The associated electricity bill increasingly dominates the overall costs related all the activities of HPC systems.

The problem is generally formulated as the need to reach a good trade-off between *time-to-solution* and *energy-to-solution*. Different approaches have emerged to solve this problem, which can be summarised as follows: vendors work on power-efficient processors and software developers on how to use them at the best [30]. However, an effective solution is possible only by properly managing all layers of the system, from the software stack to the cooling system [28]. Thus, we need power efficient software's as well as hardware integrated solutions and optimized devices.

The HPC market is growing significantly as the topic itself is becoming popular and the need for computing speed a genuine fact. The so-called "embedded HPC" is a new and emerging topic, which consists on the development and use of highly parallel micro-servers/embedded devices as mainframe computing systems [23]. These systems are increasingly used particularly in the field of artificial intelligence (AI) to support both data collection and model inference. The advantage of using embedded devices is their energy efficiency for a competitive computing performance compared to traditional CPUs. For machine/deep learning inference, a new generation of Coral Dev Bord microcontrollers can outperform traditional Intel Skylake server processors by more than 20x times on both time performance and energy efficiency[48]. This illustrate the energy efficiency and the processing speed of embedded systems over CPUs for some specifics applications. Thus, these low-power systems are widely considered as good candidates when energy is the central concern.

There are several contributions in the literature on energy in HPC and embedded systems. These works range from the definition of metrics [12, 105] to the optimization of energy [72, 110, 128] through the development of profiling and energy management tools[52, 120]. This work is carried out on the hardware and software side of the systems as well as on the algorithmic level, targeting different types of system *(embedded, CPU, GPU, FPGA and hybrid)*.

The focus on *energy* in the context of computer systems is also related to *carbon footprint*, which is a more general concern currently in the spotlight. Indeed, *energy* can be turned into *carbon emission* by multiplying it with the *carbon intensity* of the energy supply[103]. If the power consumption of most hardware components is well known or can be measured accurately, it not the case with carbon emission, which has to (roughly) estimated by specific means or using the aforementioned conversion.

In this paper, we survey a taxonomy of energy concerns in computers systems. For each type of system (general purpose computers, accelerators, embedded systems/micro-controllers and modern supercomputers), we present stat-of-the-art (SOTA) architectures with a focus on power management tools. Another contribution of this work is a survey of SOTA energy/power optimization techniques with an emphasis on AI applications and a prospective analysis on all studied systems.

The remainder of this paper is structured as follows: Section 2 presents a review of existing surveys that address the topic of energy management in HPC and embedded systems. Section 3 is about a quantitative overview of energy/power aspect in computer, with a focus on the main energy/power and carbon footprint metrics. Section 4 show an overview of most recent energy aware hardware architecture for HPC and AI workloads. Section 5 discuss about a taxonomy of energy concern in embedded systems, accelerators, general purpose computers and modern supercomputers, with a special focus on energy management and optimization tools. Section 6 discuss about cooling system technologies from the energy consumption standpoint. Section 7 present, comments and discusses some energy/power optimization techniques from the literature. Section 8 present a literature review for energy concern of AI applications in computers system. Section 9 give a short prospective analysis of this survey together with some technical recommendations. Finally, Section 10 concludes the paper.

#### 2 RELATED REVIEW WORKS

Beloglazov et al. [13] discuss about the sources and issues of high power/energy consumption, and provide a taxonomy key aspects related to energy-efficient design of computing systems, covering different levels including *hardware*, *operating system*, *virtualization* and *data center*. The main aim of their taxonomy is to guide future design and development activities.

A survey by Kocot et al. [72] investigates energy-aware scheduling methods used in modern HPC systems starting with the problem definition and then tackling various goals associated to this challenge, including a bi-objective approach that considers power and energy constraints. The work considers the standard types of HPC system (multicore CPU and GPU) together with related energy-saving mechanisms based on dynamic voltage/frequency scaling (DVFS), power capping, and other functionalities. The work uses a collection of carefully selected algorithms, classified by the programming paradigm (e.g. machine learning or fuzzy logic).

Czarnul et al. [29] provides a state of the art on energy-aware high-performance computing (*tools, techniques and environments*). They identify and classify the main approaches by *system/device types, optimization metrics*, and *energy/power control methods*. The work describes energy management tools (benchmarking, prediction, and simulation) and optimization approaches for standard devices (CPU/GPU/Hybrid) under various configurations (clusters, grids, and clouds). The authors point out the need for the unification of energy management interfaces for different architectures. Their conclusion states that we need to develop energy-aware methods for heterogeneous environments; indicates the optimization goals worth investigating based on minimizing the product of *energy* and *computing time*; and expresses the need for the validation of energy management tools.

An overview on energy-saving efforts is provided by Maiterth et al. [84], where they focused on energy/power-aware job scheduling and resource allocation as a major step towards more efficient systems. The paper considers nine large HPC centers located over three continents and the answers to eight questions from by their respective staff. Practical management procedures including *power capping*, *job killing*, and *virtual machines* are described. Moreover, the focus of the study is more engineering oriented as it does not provide any formal or theoretical aspect related to energy-aware scheduling.

A survey by Chaudhry et al. [25] addresses thermal-aware scheduling and associated techniques for green data centers. Their study focuses on the thermal and cooling aspects of tasks scheduling, where a balanced heat distribution among the racks of the server is the main objective. They indicate some metrics to evaluate thermal awareness in green data centers. In addition, they provide a thermal modeling together with effective solutions to prevent from hard-to-cool phenomena such as hot spots. They proposed two approaches: *reactive*, where the problem is fixed upon occurrence; and *proactive*, where the goal is to prevent the problem from occurring (e.g. using the thermal model of the server room followed by a proper tasks assignment on the compute nodes).

A technical report by Ramesh et al. [110] presents a taxonomy of power/energy concerns in embedded systems design. The proposed taxonomy is derived from a systematic review of the literature, where a categorization of the topics of interest is constructed. The authors considered a collection of 95 papers related to energy management from ACM, IEEE Xplore, and Springer-Link databases. Their study focuses on energy dissipation and power optimization from the standpoint of hardware devices and that of support tools for energy profiling and optimization.

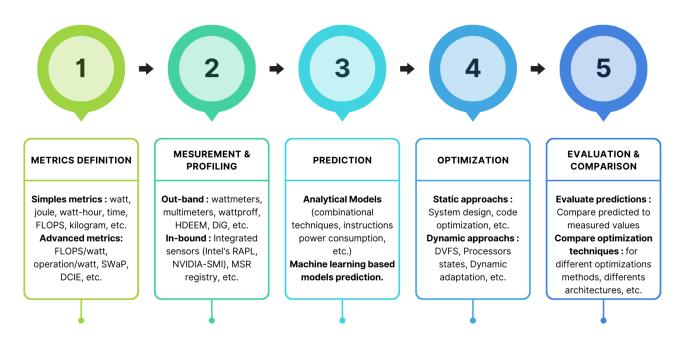

Many review works about energy concerns are generally specific to computer infrastructures (i.e., data-centers, embedded systems, supercomputer, etc.) for energy optimizations techniques, tools, and measurement. In this work, we survey the energy concern on HPC systems in a more general way considering all kind of approaches for energy/power management as presented in the taxonomy displayed in Figure 1

# **3 OVERVIEW OF ENERGY METRICS IN HPC**

The matter of appropriate energy and performance metrics has been investigated in several survey papers. However, since technology and associated features are evolving very rapidly, these studies lack some aspects that we present in this paper together with updated information related to news technologies.

There are various approaches to power measurement and different types of outputs. We can classify theses measurement approaches into two groups: Out-of-band (e.g. power meters) and in-band (e.g. RAPL counters). Out-of-band measurement is the easiest approach to consider. It uses an external device to measure power consumption without a little to no interference in the computational performance. In-band measurement requires some technical information about the target hardware and can access specific registers in a programmatic manner. Both types of measurement can be enhanced with an application-level profiling. However, it might be difficult to assess the type and detail of the measurements that are needed to obtain satisfactory insights from the energy profiling of the application. This is a major concern with the Out-of-band measurement, which uses an external device whose output data cannot be directly obtained within a program.

#### 3.1 Standard energy consumption metrics

In order to express the energy consumption at any level, we will use the most basic formula that links *energy* to *power* and *time*. The energy consumption *E* can be expressed as:

$$E = \sum_{i=0}^{n} P_i \delta_i, \tag{1}$$

where we assume a constant power  $P_i$  for time period  $\delta_i$ , with  $\delta_0 + \delta_1 + \cdots + \delta_n = T$ , where *T* is the overall time period considered. One might consider an average power *P* of the  $P_i$  over period *T* and therefore write  $E = P \times T$ . With this basic formula, we can clearly see which are the two orthogonal levers at our disposal to act on energy consumption. The variations of *P* and *T* are quite opposite, indeed the energy optimization of an HPC system is a matter of a good trade-off between the *execution time* and the *consumed power*. The goal is to optimize one while keeping the other at an acceptable level.

The reference unit of *energy* measurement according to the international system of units is the Joule (*J*). In relation with a time period, there is the watt-per-hour or watt-hour (*Wh*), with the relation  $1Wh = 3.6x10^3 J$ . In this study we will use both of them, but in most of the cases we will refer to the Watt, which is reference unit of *power* (i.e. energy consumed in a time period of 1 hour).

The first approach to get the energy consumption of a given application is to directly measure the electrical power of the targeted hardware through specific devices (*out-of-band* approach). The second approach is seek an approximation of the energy consumption using a prediction/estimation model (usually considered for performance). The first method is often used to assess the accuracy of estimation approaches.

#### 3.2 Energy metrics in supercomputers

Energy consumption is one of the major concerns when it comes to the deployment of large-scale HPC infrastructures. This must be taken into account at all levels *(from hardware to software tools)* and raises new scientific and operational challenges.

In the top500 ranking of June 2022[37], the exascale performance (both theoretical and sustained) has been reached with the FRONTIER supercomputer [99]. The exascale was an important milestone in the HPC roadmap, and this level of potential performance is the current target of several high-end HPC infrastructures. The cost associated to the energy consumption by large-scale supercomputers is noticeable and the associated carbon footprint is becoming a serious concern. The Green500 [70] consider an evaluation of the FLOPS per Watt to rank supercomputers. Correlating the two metrics, we can state that the challenge is to increase the performance per energy consumed (FLOPS/Watt). Energy-efficient computing is a multi-dimensional problem, especially in the extreme-scale computing. The electricity consumption, thus the associated bill, includes the power due to machines operation and cooling system. A 2019 estimates "A typical supercomputer consumes anywhere between 1 to 10 megawatts of power on average, which is equal to the electricity needs of almost 10,000 homes" [19]. For instance, the electricity bill paid by the RIKEN institute in 2020 for their (energy-efficient) Fugaku supercomputer was nearly \$60 millions [8]. Table 1 give some illustrative data about the electricity bill of the top five supercomputers of the november 2022 top500 ranking [37]. We assume that the whole supercomputer is running continuously during 1 hour, thus we get the estimate electricity cost (in dollars, last column) by considering the cost per KWh that applies in the geographical location of the computing center. We considered the electricity prices per country on September 2022 [44].

| Machine  | Peak Perf.   | Power  | \$/KWh | Total(K\$) |

|----------|--------------|--------|--------|------------|

| Frontier | 1.685 EFLOPS | 21.1MW | 0.150  | 3.165      |

| Fugaku   | 537.2 PFLOPS | 29.9MW | 0.219  | 6.548      |

| LUMI     | 428.7 PFLOPS | 6.02MW | 0.198  | 1.192      |

| Leonardo | 255.7 PFLOPS | 5.61MW | 0.561  | 3.147      |

| Summit   | 200.8 PFLOPS | 10.1MW | 0.150  | 1.515      |

Table 1: Electricity cost per hour for the top five supercomputers.

The so-called *thermal design power* (TDP), also called *thermal design point*, is the maximum amount of generated heat (by a computer chip or component) that the cooling system is designed to dissipate. The *power rating* (highest power input allowed) for a microprocessor is generally 1.5 times the TDP [105]. The purpose of the TDP is to provide system designers with a power target so as to guide the selection of a convenient thermal solution. Under a steady workload, the TDP is the maximum power consumption of the processors. However, during the turbo mechanism or certain

Roblex Nana, et al.

Figure 1: Taxonomy of power/energy management solutions with related approaches and tools.

types of workload such as vectors instructions, it can sometimes exceed the maximum TDP.

The so-called *Average CPU Power* (ACP), a concept defined by AMD for Opteron processors, is the average dissipated power of a processor while running a defined set of benchmarks (Transaction Processing Performance Council (TPC Benchmark\*-C), SPECcpu\*2006, SPECjbb\*2005, and STREAM) [121]. AMD indicated that these measurements to determine the ACP value are not to be considered for every processor, but only for some particular ones selected by its manufacturing units [9].

From thermal standpoint, the processor TDP specification is a critical value because any thermal solution should dissipate at the level of that rated indication. Intel and AMD both agree on this point. If a given processor design is based on the ACP, then it might be undersized and out of its thermal specifications. For servers the main concern is not on how much power a specific component dissipates, but instead the power of the entire server when running a given workload. The corresponding measurement can be easily made following and *out-to-band* approach with a power meter on the input cord(s).

SWaP (Space, Wattage and Performance) [33] is an objective three-dimensional metric that provides a more comprehensive and realistic way to evaluate servers. It is calculated considering *performance, power* as indicated by equation 2 that follows:

$$SWaP = \frac{Performance}{Space * Power},$$

(2)

where *Performance and Power* is measured by any convenient benchmarks, and *Space* is related to the size of the computer.

The so-called *Power usage effectiveness* (PUE)[12] is a metric used to determine the energy efficiency of a data center. It is determined by dividing the total amount of incoming power by the consumed power as expressed by formula 3.

$$PUE = \frac{Total\_Facility\_Energy}{IT\_Equipment\_Energy} = 1 + \frac{Non\_IT\_Facility\_Energy}{IT\_Equipment\_Energy}$$

(3)

According to the "Uptime Institute Annual Global Data Center Survey 2021" [31], PUE and power consumption are among the top tracked sustainability metrics. But in 2022, key findings reported in the Uptime Institute Global Data Center Survey 2022 [66] indicated the requirement of additional metrics to supplement PUE for future efficiency gains, which should focus on IT power. A similar benchmarking standard considered by the Green Grid is DCiE (Data Center Infrastructure Efficiency), which is just the inverse of PUE. Both metrics apply to a more global level, thus they do not capture the consumption specific to the computing activities. Indeed, information technology (IT) equipment include computing units and all associated peripherals. Nevertheless, having such a macroscopic information makes sense as all considered facilities are related to the computing activities.

A survey by Jin et al. [69] presents the state-of-the-art on green data center techniques including *energy efficiency, resource management, thermal control* and *green metrics*, with a detailed comparison among them and key challenges for future research.

### 3.3 From energy to Carbon footprint

Climate change currently stands as a critical concern because of its significant impact on ecosystems and livelihoods across the world. It's a clear fact that carbon dioxide emissions are the primary driver of global climate change. According to recent estimates, the total  $CO_2$  emissions of the information and communications technology (ICT) sector account for around 2.1%–3.9% of global  $CO_2$  emissions[39]. Therefore, estimating and reducing the carbon footprint in ICT is worth all related efforts.

The typical way for carbon footprint estimate of IT infrastructure activities is to derivative it from power consumption. The paper by Patterson et al [103] provides a valuable study of the carbon footprint of computing workloads. They stated that  $CO_2$ *equivalent emissions* ( $CO_2e$ ) accounts for *carbon dioxide* and all the other greenhouse gasses as well like *methane and nitrous oxide* for instance. This equivalent emission can be calculated from the *electric power* by multiplying it with the *carbon intensity*

of the energy supply as expressed through formula (4) [103]:

$$CO_2 e = Wh * (CO_2 e \text{ per } Wh) \tag{4}$$

*Carbon intensity* ( $CO_2e$  per Wh) is the amount of carbon dioxide ( $CO_2e$ ) that is released to produce a watt-hour of electricity. The average data-center carbon emissions in 2020 was 0.429  $tCO_2e$  (ton of carbon dioxide equivalent emissions) per MWh (Megawatt hour), but the gross  $tCO_2e$  per MWh can be 5x lower in some specific data-centers [103]. Table 2 is provided as an illustration of the carbon footprint for top ranked supercomputers. We used formula (4) and an estimation of the *carbon intensity* from 2022 data [100]. We clearly see that the floating-point performance and the necessary ( $CO_2e$ ) are not directly correlated, the hardware profile of the machines is a key factor.

| Machine  | Peak Perf.   | Power  | Kg(CO <sub>2</sub> )/KWh | CO <sub>2</sub> (kg\$) |

|----------|--------------|--------|--------------------------|------------------------|

| Frontier | 1.685 EFLOPS | 21.1MW | 0.379                    | 7 997                  |

| Fugaku   | 537.2 PFLOPS | 29.9MW | 0.479                    | 14 322                 |

| LUMI     | 428.7 PFLOPS | 6.02MW | 0.132                    | 795                    |

| Leonardo | 255.7 PFLOPS | 5.61MW | 0.372                    | 2 087                  |

| Summit   | 200.8 PFLOPS | 10.1MW | 0.379                    | 3 828                  |

Table 2: CO<sub>2</sub> per hour for the top five supercomputers.

# 4 HARDWARE ARCHITECTURE FROM THE ENERGY STANDPOINT

### 4.1 Accelerators

4.1.1 *GPU.* GPUs are specialized devices designed for efficient graphics rendering and image processing. Their parallel structure makes them more efficient than *traditional CPUs* for algorithms that process large blocks of data in parallel. Nowadays, GPUs stand as the reference accelerator in the HPC landscape. In addition to being now designed as general purpose units, GPUs have a top consideration when it comes to energy efficient in HPC [56]. From the absolute standpoint, modern GPUs consume a significant amount of power (from 50-600W or even more). However, because of their noteworthy processing speed, they show better performance-per-watt than standard CPUs for specific workloads.

AMD Instinct MI250X was ranked world's fastest HPC accelerator in 2022[3]. This GPU has a (double-precision) peak performance of 47.9 TFLOPS and a peak power between 500 and 560 TDP. A combination with cutting-edge processors yield very powerful HPC systems, like the (AMD EPYC CPU, AMD Instinct MI250X) CPU-GPU pairing of the FRONTIER (Exascale) supercomputer and other top ranked machines from the top500 list of November 2022[37]. NVIDIA H100 Tensor Core GPU [96] is the response from NVIDIA about this innovation from AMD as competitive material with 700W TDP in maximum configuration. Intel Launched *Intel Data Center GPU Max Series* project in 2022 with PONTE VECCHIO as the first competitive product for data center GPU market [63] with 600W TDP. A comparative view in terms of *flops performance* and *power supply* of the major accelerators is provided in table 3.

4.1.2 TPU. With the high computing power required for cuttingedge AI, domain-specific architectures for Neural Network computations have emerged, like the *Tensor Processing Unit (TPU)*, a Deep Neural Network (DNN) accelerator from Google. An individual Edge TPU can perform 4 trillion operations per second (4 TFLOPS) with only 2 watts of power. The latest TPU (*version 4*) has an average TDP of 192W. For illustration, the Edge TPU can execute state-of-the-art mobile vision models such as MobileNet V2 at almost 400 frames per second in a power efficient manner [46]. Pandey P. et al [102] parameterized the extreme hardware under-utilization in a TPU systolic array and proposed UPTPU: an intelligent data-flow adaptive power-gating paradigm that yields a improvement of the TPU energy efficiency by factor 3.5 to 6.5 on different input batch sizes. This ultra low power devices is nowadays integrated as an accelerator into microcontrollers (single-board unit), as we can see with *Coral Dev Board* for instance.

4.1.3 FPGA. Field Programmable Gate Arrays (FPGAs) are integrated circuits with ability to be reconfigured to implement a specific processing at the hardware level. Initially applicable to very specific domains, FPGAs has extended so as to now stand as a important components of servers and supercomputers, as well as edge computing systems[15]. However, their energy efficiency is still an important concern, with no easy or standard ways for hardware/software power management. Hosseinabady and Nunez-Yanez [55] investigate the use of FPGAs in an embedded system for energy saving. They study the energy efficiency of a hybrid FPGA-CPU device that can switch between hardware and software on periodic tasks. In addition, they successfully applied the voltage and frequency scaling (VFS) to reduce the energy consumption. Moreover, they showed that in some cases, if the task's period is higher than a specific threshold a reduction of the energy consumption cannot be obtained on the FPGA, hence the effectiveness of a software support for energy saving. Experimental results show up to 48% energy reduction by applying the proposed techniques at runtime on thirteen individual tasks. As previously said, the major accelerator in the HPC landscape remains the GPU, however the FPGA is becoming a serious candidate.

# 4.2 Embedded systems: Microcontrollers

Due to their small size and single-chip configuration (thus at the expense of processing power, memory and storage), microcontrollers have a little energy consumption while keeping a certain level of computing efficiency. Much more energy is required to power a GPUs and standard CPUs, which yields some limitations and constraints in their usage. Micro-controllers are typically not wired into main power, they instead rely on batteries or residual energy. For example, a micro-controller can run on a single coin battery for weeks or even months. However, having a low power system does not yield lower energy consumption by itself. Indeed, it is important to optimize the software, not just in terms of functionality or processing efficiency, but also with respect to energy efficiency. We now describe some of the major devices of embedded computing.

4.2.1 Arduino. When it comes to microcontrollers and embedded systems, one of the first candidate that pops is *Arduino*. Arduino is an open-source electronics platform based on easy-to-use hardware and software for ultra low power chips, which consumes less than a single watt of nominal power. The Arduino Portenta H7 [7] is currently the most powerful IoT Cloud compatible boards of the Arduino series. Arduino can be used to connect devices, visualize data, control and share projects online. Beginners and advanced users can meet their specific needs from

| Name                | RAM (GB) | core frequency | TDP (w)    | Peak TOPS             | peak         | performance/ |

|---------------------|----------|----------------|------------|-----------------------|--------------|--------------|

|                     |          | (GHz)          |            |                       | TFLOPS(fp32) | watt (INT8)  |

| Tesla A100 SXM4     | 80       | 1.41           | 400        | 312(bf16)/624(int8)   | 19.5         | 1.56 TOPS/W  |

| Tesla H100 SXM5     | 80       | 1.98           | 700        | 1000(bf16)/2000(int8) | 60           | 3.33 TOPS/W  |

| AMD Instinct MI250X | 128      | 1.7            | 560        | 383 (bf16 or int8)    | 95.7         | 0.68 TOPS/W  |

| Intel Ponte Vecchio | 128      | 1.6            | 600        | 720(bf16)/1440(int8)  | 45           | 2.40 TOPS/W  |

| Google TPU v4       | 32       | 1.05           | 192 (idle) | 275 (bf16 or int8)    | /            | 1.43 TOPS/W  |

Table 3: SOTA accelerators systems characteristics

its wide range of features and possibilities. However, even with Portenta H7, Arduino is not powerful enough to handle HPC workloads in the context of embedded systems as compared with others microcontrollers (see Table 4).

4.2.2 Raspberry Pi. While Arduino is an electronic board with a simple microcontroller, Raspberry Pi is a full-fledged computer. Unlike Arduino, Raspberry Pi has its own operating system, thus it can carry out more complex operations (e.g. *robot control* and *weather monitoring*, to name these two). The Raspberry Pi 4 Model B [112] is the latest model of the Raspberry Pi microcontrollers series. It offers a noteworthy increase in processing speed, multimedia performance, memory and connectivity over the previous generation (Raspberry Pi 3 Model B+), while keeping full compatibility with earlier versions and same level of power consumption. The Model B offers a level of performance comparable to that of entry-level x86 PC systems but with the advantage of energy efficiency as it has a maximum nominal power of 10W.

4.2.3 Intel NCS2. Intel Neural Compute Stick 2 (Intel NCS2)[64] is a plug-and-play Development Kit for AI Inference. NCS2 is based on an Intel Vision Processing Unit(VPU) chip named Movidius X. Movidius provides its Neural Compute Stick (i.e. Fathom) to bring a basic-level deep learning capabilities into embedded devices. It can be used to develop, fine-tune, and deploy convolutional neural networks (CNNs) on low-power applications that require real-time inference. It supports heterogeneous execution across computer vision accelerators (CPU, GPU, VPU, and FPGA) using a unified API. Its so-called Vision Processing Unit (VPU) includes vision accelerators, a Neural Compute Engine, imaging accelerators, and 16 SHAVE vector processors paired with a CPU in one heterogeneous package. The combination of the aforementioned units provides a total of up to 4 TFLOPS with 1.5W of power [106]. However, Intel is discontinuing this product and its technical support will continue until June 30, 2023, while warranty support will continue until June 30, 2024[64]

4.2.4 Nvidia Jetson. The Jetson Nano Developer Kit [95] is the most popular board from Nvidia Jetson series. It delivers a note-worthy processing capability to efficiently support high-performance AI at low power and cost. The developer kit can be powered by micro-USB and comes with extensive I/Os. This makes it simple for developers to connect a diverse set of new sensors to enable a variety of applications at a little power of 5 watts. The Jetson AGX Orin Developer Kit [97] is currently the most powerful board from this series, with up to 275 TOPS for running the NVIDIA AI software stack. It enables to create advanced robotics and edge AI applications. But this performance incurs a higher cost with currently more than 2000\$ for 60W TDP.

4.2.5 *Coral Dev Board.* The Coral Dev Board[47] is a singleboard computer with a removable system-on-module (SOM) that contains eMMC, SOC, wireless radios, and Google's Edge TPU. It's perfect for IoT devices and other embedded systems that demand fast on-device ML inferencing. Coral dev is also the most efficient out of all the microcontrollers we have found. With on board TPU, it is capable of performing 4 tera-operations per second (TOPS), using 0.5 watts for each TOPS (2 TOPS per watt)[48]. The USB version can be connect to any system running Debian Linux (including Raspberry Pi), macOS, or Windows 10. Coral Dev is very fast but, with bad tech support, faulty units and seems like a very common problem.

### 4.3 General Purpose Processors

4.3.1 x86 based processors. x86 is a family of CISC instruction set architectures, initially developed by Intel from Intel 8086 microprocessor and its 8088 variant. It was introduced in 1978 as a fully 16-bit extension of Intel's 8-bit 8080 microprocessor, with memory segmentation as a solution for addressing more memory than can be covered by a plain 16-bit address. Embedded systems and general-purpose computers used x86 chips before the IBM Personal Computer in 1981. Nowadays, most desktop, workstation, laptop and server computers are based on the x86 architecture family, while mobile categories such as smartphones or tablets are dominated by ARM. The fastest supercomputer in the TOP500 list for November 2022 (FRONTIER) is built with AMD Epyc CPUs that are based on the x86 ISA. The market of CPUs in the HPC landscape and data centers is still dominated today by x86 CPUs.

AMD claim that its EPYC processors power the most energyefficient x86 servers, delivering exceptional performance with lower energy consumption [4]. AMD EPYC 9654 servers shall use up to 29% less annual power than Intel Xeon Platinum 8490H servers at the same performance, while helping reduce capital expenditure up to 46% [4]. Note that these two CPU models require respectively 350W and 360W for Intel and AMD CPUs respectively.

4.3.2 ARM based processors. Energy saving has become one of the main challenges for new generation servers and supercomputers. Many manufacturers of HPC systems consider low-power ARM components that are also present today in the vast majority of embedded or mobile systems. Indeed, the particularity of ARM components is their low energy consumption with a competitive processing performance as Intel and AMD x86 architectures. Several international collaborative projects like the Japanese Post-K, the European Mont-Blanc, or the UK's GW4/EPSRC, announced the adoption of ARM technology for their high-performance computing (HPC) systems [85]. On November 2018, for the first time, an ARM-based system was listed in the Top500 ranking. It was the Astra[136] supercomputer powered by Marvell's ThunderX2 ARM CPU and hosted at the Sandia National Laboratories (USA).

| Name                | memory(GB) | core fre-    | TDP (w) | Peak TOPS   | peak TFLOPS(fp32) | performance/watt |

|---------------------|------------|--------------|---------|-------------|-------------------|------------------|

|                     |            | quency (GHz) |         |             |                   |                  |

| Raspberry Pi 4B     | 8          | 1.5          | 10      | /           | 0.135             | 2.02 GFLOPS/W    |

| Jetson Nano         | 4          | 1.43         | 10      | 0.472(int8) | 0.236             | 0.047 TOPS/W     |

| Jetson AGX Orin     | 64         | 2.0          | 60      | 275(int8)   | 5.3               | 4.58 TOPS/W      |

| Arduino Portenta H7 | 0.008      | 0.48         | 1.15    | /           | /                 | /                |

| The Coral Dev Board | 4          | 1.5          | 0.65    | 4(int8)     | /                 | 2 TOPS/W         |

| Intel NCS2          | 8          | 0.7          | 1.5     | 4(int8)     | /                 | 2.66 TOPS/W      |

Table 4: Characteristics of selected state of the art embedded systems

| Name                 | memory(GB) | core frequency | TDP (w) | Peak TOPS  | Peak GFLOPS | performance/watt |

|----------------------|------------|----------------|---------|------------|-------------|------------------|

|                      |            | (GHz)          |         |            | (fp64)      |                  |

| Intel Platinum 8490H | 4000       | 1.9            | 350     | /          | 3 648       | 10.42 GFLOPS/W   |

| AMD EPYC 9654        | 6000       | 2.4            | 360     | 7763(int8) | 3 686       | 10.23 GFLOPS/W   |

| Fujutsu A64FX        | 32         | 2.6            | 150     | 3.4(int8)  | 3 400       | 22.66 GFLOPS/W   |

| Marvell ThunderX2    | 512        | 2.2            | 180     | /          | 563         | 3.12 GFLOPS/W    |

|                      | m 11       | F SOTA O       | 1       |            |             |                  |

Table 5: SOTA General purpose computers characteristics

# **5 ENERGY MANAGEMENT TOOLS**

# 5.1 Energy tools for GPUs

*NVIDIA-SMI (NVIDIA System Management Interface)* [94] is a command line utility for the management and monitoring of NVIDIA GPU devices that is based on the NVIDIA Management Library (NVML). The tool can be used to set the power range (max and min, in Watt) of the execution of a given application. Its GPU Operation Mode (GOM) allows to reduce the power usage and optimize the GPU throughput by disabling some features accordingly. It also implements a power scaling algorithm to dynamically reduce the clock frequency when the GPU is consuming too much power.

#### 5.2 Energy tools for CPUs

- Intel RAPL[65](Running Average Power Limit Interface) is an interface for reporting the (accumulated) energy consumption of various system-on-chip (SoC). The RAPL's energy reporting feature has been available on many generations of Intel SoC products. Intel processors utilize this energy information for internal SoC management purposes such as the control of power limits in association with the Turbo Boost power limit settings. Energy information from the RAPL interface gets updated every 1 ms, which is several orders of magnitude slower than what physical side channel probing could achieve. RAPL measurements ignore a large part of the power consumption of servers because they focus on CPU and RAM. Some experiments on Intel processor from Grid5000 [51] show that it just represent 42% of the overall servers consumption [5].

- AMD RAPL counters : Concerning Zen architecture, AMD replaced APM (Application Power Management) with RAPL. The implementation is similar to the corresponding Intel's RAPL, but uses different control registers. While Intel typically provides multiple domains and the option to limit power consumption over various time frames, AMD only considers registers for memory reads and core power consumption. However, the latter is available with a per-core spatial resolution, while a per-package applies for Intel's core domain. Schöne et al. [118] highlighted various energy efficiency aspects of the AMD Zen 2 micro-architecture in order to facilitate system comprehension and optimization. Key findings include qualitative and quantitative descriptions regarding *core frequency transition delays*, *workload-based frequency limitations*, and *effects of I/O die P-states on memory performance*. The authors made a comparative study with some high-end Intel architectures (i.e., Cascade Lake, Skylake, Haswell) for power efficiency and provided details on power measurements accuracy on both architectures. The work shows that AMD RAPL is unsuitable to optimize the overall energy consumption. Their approach failed on reflecting the influence of the operands, which can also be seen as a benefit when it comes to side-channel attacks that are based on power measurement.

- For ThunderX2[86] chips, there is no RAPL counters but there are other *harware specific* on-chip sensors. These sensors are not yet supported by common libraries like PAPI[17], perftools[38] for instance. However, Marvell[86] has provided an tool named *tx2mon* [87], which is based on the Linux kernel driver *tx2mon\_kmod* to provide access to specific system data and allow to configure the way to measure energy.

- *Model-Specific Register* (MSR) is any of the various control registers in the x86 architecture used for debugging, program execution tracing, computer performance monitoring, and toggling certain CPU features.

- ACPI (Advanced Configuration and Power Interface)[130] is an open standard that the operating system can use to discover and configure the components of the computer, to perform power management, auto configuration, and status monitoring. ACPI defines the performance states, designated by P-States. P-States correspond to different performance levels that apply while the processor is actively executing instructions according to energy saving and performance trade-off scenarios. Each system manufacturer decides its way to implement this specification standard to save energy in the system. For example, Intel CPUs, regarding Haswell architecture, provides voltage regulators per core, thus each core has its own P-State.

- Device Tree (DT)[80]: While ACPI was historically created for x86 platforms, the ARM ecosystem developed "Device Tree" (DT) to describe the same information for ARM-based devices. Thus, ACPI and DT overlap in that they both provide mechanisms for enumerating devices and attaching additional configuration data

| Name                 | type     | Objective        | Techniques              | Portability                    |

|----------------------|----------|------------------|-------------------------|--------------------------------|

| NVML(NVIDIA-MSI)[94] | Software | power management | Dynamic Power Man-      | Linux with Nvidia GPU de-      |

|                      |          |                  | agement, Power capping, | vices; never tested it on Win- |

|                      |          |                  | Sampling measurement    | dows                           |

Table 6: SOTA accelerators energy/power management tools

to devices (which can be used by higher layers of software). The biggest difference between DT and ACPI is that DT is effectively a structured mechanism for passing arbitrary data, while ACPI provides standardised data.

- PAPI (Performance API) [17] library is a platform independent tool which provides developers with an interface and methodology for gathering performance-related hardware data. The basic principle is to allow developers to see the relation between the software performance and corresponding processor events. McCraw et al. [88] extended PAPI to measure and report energy and power values even on complex architectures.

- Intel Power Gadget [61] is one of the most easy-to-use energy profiler. It provides a graphical user interface with a few plots showing CPU and DRAM utilisation (%), cores frequency (GHz), temperature (°C), and power consumption (W). The total energy consumption of the CPU and DRAM written into files (i.e. *Log files*). When installing Intel Power Gadget, its command-line interface (named PowerLog) is also installed.

- Powerstat [26] is an easy-to-use tool to measure energy consumption on Linux. Intel Power Gadget and PowerLog are not compatible for Linux system, so Powerstat was developed similarly to the previous tools. Powerstat is just another wrapper around an Intel library RAPL. However, it provides a simple interface for a command-line usage.

- PowerTOP[62] is a Linux tool used to diagnose issues with power consumption and power management. In addition to being a diagnostic tool, PowerTOP also has an interactive mode that can be used to handle various power management settings in case the direct mode is restricted by the OS. Its main advantage is the ability to estimate the energy consumption of the considered machine. It provides an interactive mode to fine-tune power management settings in Linux system.

- Perf tools[38]: A very quick and easy way to obtain the energy consumption of a program in a Linux environment, is through Perf. It is a command-line tool that offers a wrapper to Intel's RAPL. It facilitates the collection of energy measurements of the components of a computer and associated devices.

- Another quick way of getting energy and power measurements for Intel processors is through Likwid[129]. Likwid uses the RAPL interface, developed by Intel, to fetch energy and power measurements from different types of CPU. Compared to Perf, Likwid does not offer an option to run a given test several times. However, it provides *power* estimation in addition to energy measurement. Moreover, Likwid offers other options such as thread's temperature monitoring.

- PyJoules[59] is a software toolkit written in Python to measure the energy footprint of a given host machine. It monitors the energy consumed by a specific device of the host machine. It works ionly with intel CPUs, RAM (for intel server architectures), intel integrated GPUs and nvidia GPUs.

#### 5.3 Energy tools for microcontrollers

- EEMBC CoreMark-Pro [36] is a benchmark that aims at becoming the industry standard for embedded platforms. It contains five (resp. four) prevalent integer (resp. floating-point) workloads. The workloads in CoreMark-Pro represent a wide variety of performance characteristics, memory utilization, and instruction-level parallelism, highlighting the strengths or and weaknesses of the target processor in term of performance and energy efficiency.

- EEMBC ULPBench [35] is a benchmark whose the goal is to overload a given processor in order to help determining the maximal amount of energy consumed. The benchmark consists of a number of mathematical and sorting operations. The STMicroelectronics PowerShield provides the backbone of the framework for probing an embedded system energy measurement.

- Dr. Wattson [131] is an Energy Monitoring Module for high quality energy monitoring and measurements for microcontrollers boards. It is coupled with easy to use Arduino and Python libraries to provide quality AC energy data like *RMS Current*, *RMS Voltage*, *Power Factor*, *Line Frequency*, *Active/Apparent Power*, with just a few of lines of code.

- PSoC (Programmable System on Chip) 5LP[68] is a data acquisition (DAQ) system for measuring and analyzing the power consumption of microcontrollers. DAQ system consists of a current measurement circuit using potentiostat technique (i.e, apply constant voltage during experiment). The DAQ device is based on system on chip PSoC 5LP and Python program for the analysis, storage and visualization of measured data. Implemented DAQ device is connected with a computer through a USB port and tested with developed Python program.

-  $N^3$  profiler [34] is a power consumption monitoring tool to detect anomalies in power consumption for ARM-Based embedded systems at the level of the components. The authors used NARX (Nonlinear AutoRegressive eXogenous) [16] neural networks model as estimator to monitor energy/power for profiling and diagnosis purposes.  $N^3$  improves upon the accuracy reported in the literature while maintaining low power and computational overhead. Experimentation was done on a smartphone considered as an embedded device.

**Comment :** For a more accurate power measurement on micro-controller board, the following actions can be considered: disable HDMI and LEDs if present; minimize accessories usage (a connected keyboard for instance); be selective with Software (different programs running) and disable WiFi. Different system commands can be used depending on the micro-controller to disable the aforementioned features.

### 5.4 Energy tools for Modern HPC systems

- HDEEM (High Definition Energy Efficiency Monitoring)[52] is an FPGA-based system on-chip that is intended to equip a compute node for its power measurement. The aim is to aggregate at high frequency (1 kHz) the measurements made by watt-metrics probes distributed among the components of the compute node.

| Name                          | Туре          | Objective              | Techniques              | Portability              |

|-------------------------------|---------------|------------------------|-------------------------|--------------------------|

| RAPL counters[65]             | hardware      | power management       | Dynamic Power Man-      | x86 CPU                  |

|                               |               |                        | agement, Power capping, |                          |

|                               |               |                        | Sampling measurement    |                          |

| ACPI[130]                     | specification | power management       | Dynamic Power Manage-   | x86 CPU                  |

|                               |               |                        | ment, Power capping     |                          |

| DT[80]                        | specification | power management       | Dynamic Power Manage-   | ARM CPU                  |

|                               |               |                        | ment, Power capping     |                          |

| Perf tools[38]                | software      | performance and energy | interface to hardware   | Linux with Intel devices |

|                               |               | management             | counters                | for energy               |

| PAPI[88]                      | software      | performance and energy | interface to hardware   | All Linux systems        |

|                               |               | management interface   | counters                |                          |

| Likwid-powermeter[129]        | software      | power profiling        | query RAPL counters     | Linux devices with Intel |

|                               |               |                        |                         | processor                |

| PowerTOP[62]                  | software      | energy monitoring      | query Intel RAPL        | Linux with AMD or Intel  |

|                               |               |                        |                         | devices                  |

| PyJoules[59]                  | software      | energy monitoring      | query RAPL and Nvidia   | Linux with AMD, Nvidia   |

|                               |               |                        | SMI interfaces          | or Intel devices         |

| Powerstat[26]                 | software      | measure energy con-    | query Intel RAPL        | Linux on Intel PCs       |

|                               |               | sumption               |                         |                          |

| Power Gadget and PowerLog[61] | software      | energy/power and tem-  | query Intel RAPL        | Mac or Windows on Intel  |

|                               |               | perature monitoring    |                         | PCs                      |

| tx2mon[87]                    | software      | energy/power and tem-  | query hardware counters | Marvell ThunderX2        |

|                               |               | perature monitoring    |                         |                          |

Table 7: SOTA General purpose computers tools for energy/power management

| Name               | Туре                  | Objective              | Technique                | Portability                |

|--------------------|-----------------------|------------------------|--------------------------|----------------------------|

| EEMBC CoreMark[35] | software              | system benchmark for   | stress CPU with specific | 8 to 64-bit microcon-      |

|                    |                       | energy consumption     | workload                 | trollers                   |

| EEMBC ULPMark[35]  | software              | system benchmark for   | stress CPU with specific | 8, 16 and 32-bit microcon- |

|                    |                       | energy consumption     | workload                 | trollers                   |

| PSoC 5LP[68]       | software and hardware | system benchmark for   | SoC Module based on      | all microcontrollers       |

|                    |                       | energy consumption     | PSoC and python pro-     |                            |

|                    |                       |                        | gram                     |                            |

| Dr. Wattson [131]  | software and hardware | Energy Monitoring      | SoC Module based on Ar-  | Arduino, Raspberry         |

|                    |                       |                        | duino and python pro-    | and simillars microcon-    |

|                    |                       |                        | gram                     | trollers                   |

| $N^{3}[34]$        | software              | Monitoring, diagnosis, | machine learning predic- | embedded systems           |

|                    |                       | software optimization  | tion                     |                            |

Table 8: SOTA Embedded systems energy/power management tools.

The samples associated to the last 7 hours of execution can be stored in a local memory of HDEEM for direct accesses through a programming interface in C language and/or through reads from report files.

- Similar to HDEEM, WattProf[111] is a system-on-chip based on an FPGA that can be connected via a PCIe interface to a compute node. WattProf comes with dedicated wattmetric probes that can be plugged on the PCIe interface of the targeted hardware components and also on the connectors for the DRAM. WattProf includes a memory for storing samples of energy consumption measurements, and an API to access those samples.

- DiG (Dwarf in a Giant) [78], is another system on-chip based on an Arduino 5. Unlike HDEEM and WattProf, DiG connects to the power supply of the computer and thus captures its overall energy consumption rather than that of individual components. The Arduino board is used to process the energy consumption data, as well as to send them out through the network of the supercomputer. It might be more convenient or efficient to dedicate an individual unit to the management of the measurements coming from the participating compute nodes. That unit will thus serve as the provider of energy measurements to the user. In addition, DiG also allows for accurate and high frequency sampling, while remaining a low cost system-on-chip for HPC.

- PowerPack [42] was the first tool to isolate the power consumption of common devices including *disks, memory, NICs*, and *CPU* within a given machine and correlate the corresponding measurements with the main subroutines of the applications being profiled. The framework support multi-core and multiprocessorbased nodes and provides in-depth analyses of the energy consumption of parallel applications. These analyses include the impacts of multiprocessing at the level of the chip on energy efficiency. The authors used the framework to study the power dynamics and energy efficiencies of DVFS techniques on clusters, and the experiments showed that DVFS scheduling can intelligently enhance system energy efficiency while maintaining processing performance. They claim that their methodology as described in their work can be extended to other architectures and measurement devices. For instance, one can directly use the power sensors integrated in emergent computer systems for a more convenient power measurement.

- BDPO(Bull Dynamic Power Optimizer)[123] is a dynamic reconfiguration tool that runs as a daemon behind a given HPC application and adapts the clock frequency of the CPUs according to the workload. It has the particularity of being completely agnostic to the considered application, as well as to the platform, while not requiring any configuration from the user. The authors of the tool experimentally got that the use of BDPO reduces the energy consumed by the execution of NEMO and HPCG applications by about 15%, while maintaining the associated overhead below 4% [123].

- Phase-TA [123] is a tool for analysing the profiles of iterative HPC applications, especially those produced by Bull Dynamic Power Optimizer (BDPO) [123] (see the previous paragraph). It detects locally periodic behaviours and try to characterise them by constructing patterns corresponding to the associated periodicities. The authors experimentally showed that the patterns constructed by Phase-TA are relevant representations of the considered periodicities, which seem to dominate the execution time. The observed performance of Phase-TA allows to consider the use of Phase-TA during the execution of an HPC application for its energy monitoring.

- PMAC (Power Monitoring and Controlling) Tool [21] is a web-based power monitoring and controlling tool for energy optimization of HPC applications. PMAC reports the power consumption of the sofatwer as well as for the hardware in real-time. It allows to manages power based on application's profile and DVFS mechanism. The specificity of the tool is that it can be used as an energy profiling as well as an energy optimizer. In the latter case, the tool uses its own profile report to guide the power optimization strategy. Experimental results have shown an energy saving of 12 -15% when using P-MAC. P-MAC uses CMAF (C-DAC Multi-Agent Framework) for the transmission and execution of control policies.

- EAR (Energy Aware Runtime) [77] is an energy management framework for *energy measurement, energy management* and *energy optimization*. EAR supports standard CPUs as well as (NVIDIA) GPUs. It is constantly being enhanced to support other and upcoming technologies as well. The optimization of the energy consumption of an HCP cluster is done at two levels: the *compute node level*, which is provided by the EAR library and the *system level* for power caping using DVFS techniques.

- EERT (Energy Aware Rescheduling Tool)[20] is another energy management tool that act on the internal scheduling of HPC applications in order to the reduce energy consumption through maximizing the CPU utilization and switching off idle nodes. The benefit is more noticeable when there is a important imbalance in the distribution of workloads over the nodes. EERT seamleslly uses the *distributed multithreaded check-pointing (DMTCP)* mechanism for check-pointing. Experimental results provided by the authors show 15% energy saving when using EERT.

- FIRESTARTER [120], is a handy utility that aims at creating near-peak power consumption on standard compute nodes. It can be used for tests of cooling and power infrastructures, system stability test, or as a maximum power consumption baseline for application energy efficiency studies. FIRESTARTER is currently only available for the Linux operating system and has supports for Intel architectures (Nehalem, Westmere, Sandy Bridge, Ivy Bridge, Haswell, Broadwell, Skylake, Knights Landing), AMD family 15h and 17h (Zen, Zen+, Zen 2) processors, and NVIDIA GPUs. The tools stresses the most important *power consumer* parts of compute nodes: CPU (cores + memory related components such as the caches), GPUs, and main memory and report some metrics that include power consumption.

- lo2s [57] is a lightweight performance monitoring tool. The tool collects performance and energy data w.r.t various metric (i.e., perf counters, kernel trace-points, model specific registers, and custom metric data provided by plugins). These trace data are stored in the Open Trace Format 2 (OTF2) that can be used for offline analysis using tools like Vampir [71]. Ilsche et al.[58] investigated improvements of lo2s by combining a detailed recording of system events with information from a high-resolution power measurement in the process of recording the scheduling of applications and C-state transitions.

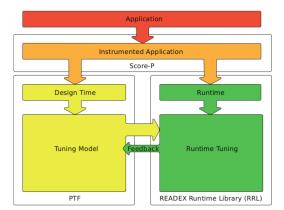

- READEX [98] is a tool suite that supports users to improve the energy-efficiency of their HPC applications. It enables them to exploit the dynamic behaviour of their applications by adjusting the system to the actual resource requirements and thus improves energy-efficiency and performance. It uses a multi-agent based approach to identify runtime situations and to determine optimal system configurations. The tools also provides insights for the specification of domain knowledge to improve the automatic tuning impact. The result of the analysis step guides runtime tuning. Figure 2 provides an overview of READEX working diagram.

Figure 2: READEX working diagram

- MERIC [119, 134] is Lightweight C/C++ library (with an interface for Fortran applications) that measures energy consumption and timings of annotated regions inside a user application. The MERIC library evaluates application behavior in terms of resource consumption and runtime parameters including *Dynamic Voltage and Frequency Scaling* (DVFS) and *Uncore Frequency Scaling* (UFS). It performs dynamic application tuning following the READEX approach. The library was originally developed for Intel x86 systems, but additional supports for AMD, IBM and selected ARM systems chips was added. It also supports HDEEM and DiG hardware tools for energy measurement. A tool called RADAR VISUALIZER [134] for visualization of the analyzed application behavior in different system configurations was proposed to analyze MERIC results.

| Name             | Туре     | Objective                    | Technique                       | Portability               |

|------------------|----------|------------------------------|---------------------------------|---------------------------|

| WattProf[111]    | hardware | energy/power measurement     | system on-chip based power      | all server node           |

|                  |          |                              | monitoring board                |                           |

| HDEEM[52]        | hardware | power measurement            | system on-chip based power      | all server node           |

|                  |          | -                            | monitoring board                |                           |

| DiG[78]          | hardware | energy monitoring            | system on-chip based power      | all server node           |

|                  |          |                              | monitoring board                |                           |

| PowerPack[42]    | software | energy/power measurement     | isolate power consumption of    | Linux systems             |

|                  |          |                              | devices in measurement          |                           |

| EERT[20]         | software | power management             | dynamic rescheduling, core us-  | Linux HPC systems         |

|                  |          |                              | age maximization                |                           |

| Phase-TA[123]    | software | energy profiling             | analysing the profiles of HPC   | Linux systems             |

|                  |          |                              | applications                    |                           |

| PMAC[21]         | software | power management             | DPM and DVFS techniques;        | Linux systems             |

|                  |          |                              | web based monitoring            | -                         |

| BDPO[123]        | software | power optimization           | DFS on computing cores dur-     | Linux x86 systems         |

|                  |          |                              | ing workloads execution         |                           |

| lo2s[57]         | software | performance and energy pro-  | Sample hardware counters        | Linux x86 systems         |

|                  |          | filing                       | events                          |                           |

| EAR[77]          | software | energy management            | DPM techniques, power cap-      | Linux with Intel, AMD and |

|                  |          |                              | ping, On/Off policies           | Nvidia devices            |

| READEX[98]       | software | energy and performance opti- | exploit the dynamic behaviour   | Linux x86 and ARM systems |

|                  |          | mization                     | of application and make re-     |                           |

|                  |          |                              | sources allocation              |                           |

| MERIC[134]       | software | energy management            | dynamic application tuning      | Linux x86, ARM and Nvidia |

|                  |          | _                            | and hardware energy measure-    | GPUs systems; HDEEM and   |

|                  |          |                              | ment                            | DiG supports              |

| FIRESTARTER[120] | software | benchmark tests of cooling   | stress execution units and data | x86 CPU and GPU           |

|                  |          | and maximum power con-       | transfer between cores and      |                           |

|                  |          | sumption                     | memory hierarchy                |                           |

Table 9: SOTA Supercomputers systems tools for energy/power management

# 6 ABOUT COOLING SYSTEMS

Designing computers that perform tasks efficiently without overheating is a major consideration for all manufacturers nowadays. Current CPUs and GPUs has a power consumption from tens to hundreds watts. Some specific CPUs consume little power like those of embedded systems and mobile devices (few milliwatts or microwatts). Computers consume electrical energy and dissipate part of it in as heat coming from the resistance in the circuits. Excessive heat is a clear threat for the integrity of hardware components, with the risk of leading to serious damage. Thus, *cooling system*, which can be internal or external, is crucial in order to cap cap the dissipated heat so as to avoid a critical overheating.

# 6.1 Cooling technologies for HPC systems

Cooling is crucial to HPC systems, especially for large-scale ones, but choosing the right technology depends on several factors like the *desired temperature* limits and the *operating cost*. There are mainly four types of cooling that are commonly considered: *air cooling, liquid cooling, rear door heat exchanger (RDHX)* and *immersive cooling.*

- **Air cooling** is the most basic cooling mechanism and also the most used one. With cheapest infrastructure costs, air cooling relies on a fan to take heat away from components. This solution is not sufficient for large-scale HPC, as users require increasingly dense computing solutions, which generate more heat per rack of servers. - Liquid cooling needs less energy to operate and it stands as the best cooling option because liquid has the ability to transfer heat much more efficiently than air[139]. In addition, it is a more ecological approach on a global viewpoint. Moreover, ambient heat removed from systems can then be used for a heating solution, thereby enhancing or replacing traditional heating systems[27].

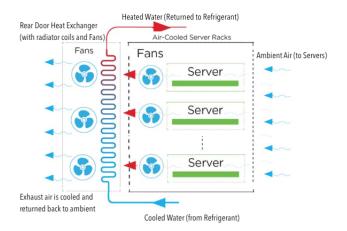

- Rear Door Heat Exchanger (RDHX) is a cooling approach that combines both air and water cooling mechanisms. It has shown a great efficiency on data centers as it acts at the level of the rack, thus it wide and increasing consideration[117]. Technically, chilled water is fed to a coil or backplate inside the RDHX, then rack-mount devices eject the hot exhaust air through the RDHX, transferring the heat to the water and ejecting cool air out of the RDHX. The RDHX can be configured in two ways: active or passive. The benefits of RDHX include [1]: Energy Efficiency (it can save up to 80% of cooling on the racks and 50% on the overall data center operation); Heat Removal (Heat transfer is more extensive since it is very close to the heat source.), less Space Requirement (uses minimum floor spaces), Flexibility (it has a more basic operation and is easier to install ) and ow maintenance (light and less frequent efforts and needed). Heat is removed from a system by putting the coolant in direct contact with hot components, and circulating the heated liquid through heat exchangers. Figure 3 gives an overview of how an RDHX works.

Figure 3: RDHX main principle

- **Immersion cooling** considers a direct immersion of the hardware in a dielectric (but thermally conductive) liquid (also called *coolant*), which then circulated through heat exchangers. The system absorbs the heat (from the source) and drives it out to the environment through a single-phase or two-phase system[101]. Some advantages of the immersion cooling include a *high heat transfer coefficient, stable hydrodynamic flow*, and *fast/direct cooling with liquid*. While immersion cooling can theoretically deliver the highest performance and PUE, it is seen by some ones as too troublesome for their HPC installations, as it can make the replacement of components tricky[27].

#### 6.2 News trends in liquid cooling design

The market for high-performance cooling systems has grown significantly as technology has shifted from simple air cooling to solution using liquid (including immersion cooling). Water is still the standard for most HPC users as it provides a good balance between performance and set-up cost.

While there are various variants, the basic concept remains the same. Water is pumped through a closed system up to a back plate placed near the hot components. Water has a better thermal conductivity, so this is potentially a higher performance system, but requires additional infrastructure. For example, many watercooled data centres have a raised floor, so so that all the pumps can be conveniently routed and driven to the targets.

Meyer and Wettig. [89] developed *iDataCool*, an HPC architecture based on *IBM's iDataPlex* platform, whose air-cooling solution was replaced by a custom water-cooling solution. A significant portion of the energy spent on HPC systems can be recovered in the form of chilled water, which can then be used to cool other parts of the computing center. The authors illustrated the cooling performance and the energy reuse efficiency through benchmarks.

Nonaka et al. [93] provided a quantitative and systematic analysis of the impact of the cooling water temperature onto HPC infrastructures. They evaluated the efficiency of the hot water cooling technique, taking into consideration not only the energy reduction on the facility side (cooling system), but also the impact on the power consumption and on the performance degradation from the machine side. They shwoed that, contrary to the gain in the energy consumption, on the HPC facility side, when using higher temperature cooling water, there is an increase in the number of nodes suffering from performance degradation, especially at synchronization barriers.

Ljungdahl et al. [81] developed a decision support model that takes basic information regarding a given cluster or data center as inputs and provides a parameterized output that shows different configurations and design parameters that can be utilized for the system. The main outputs include energy savings, cost savings and efficiency gains through the Power Usage Efficiency(PUE) and the Energy Reuse Efficiency(ERE). An electricity saving between 8.14% and 10.8% and a waste heat recovery of 85 to 576 MWh/year were obtained in a Danish case study. Additional system configurations beside existing local heating source showed an energy saving of 332%. The goal of the decision support model is to assist the design of future waste heat recovery applications through selection of system parameters including coolant temperatures, energy storage design parameters, District Heating supply temperatures and District Heating load coverage from the data center or HPC cluster.

# 7 ENERGY OPTIMIZATION TECHNIQUES

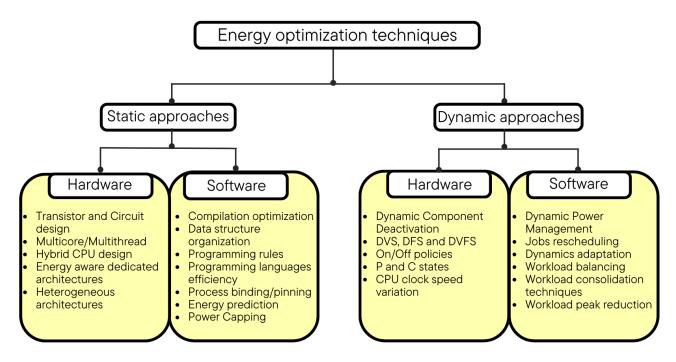

The power optimization techniques aim at minimizing the energy consumption besides traditional metrics like computing time or memory space. This concern is crucial when there is a power constraint as when the available energy is limited or its supply is costly. Power optimization can be addressed through hardware and software approaches, considering static or dynamic strategies. Figure 4 gives an overview of existing energy optimization techniques grouped by their nature.

### 7.1 Static energy optimization approaches

- *Hybrid CPU design* : Hybrid design in CPU is an approach that combine low power/performance and high power/performance cores. This was introduced by ARM with BIG.LITTLE architecture and similarly considered more recently by Intel with "Lake-field" chip [60]. Intel 12th generation CPUs (family code name: "Alder Lake") are designed following this hybrid model for energy saving and battery long life for laptop computers.

- *Programming languages efficiency*: Pereira et al [107] studied the energy efficiency of 27 programming languages, monitoring their performance using ten different programming problems. Out of these 27 selected languages, Python ranked 26. Python used 59x more energy than the most efficient language, which is the C language. Nowadays, Python might be the best choice is many cases, for instance when building and training neural networks. There is a significant potential energy saving when considering a more energy efficient language. The authors showed interesting findings such as slower/faster languages consuming less/more energy and how memory usage influences energy consumption.

- *Programming aspects* : A practical approach to C++ was presented in the work by Meyers et al. [90] that describes the basic rules followed by experts (i.e., the things they do or avoid as much as possible) to produce clear, correct, efficient code. This is a static optimization technique for time-to-solution and energy-to-solution by considering the best programming practices.

- *Machine learning prediction models* : Gao et al. [41] developed a neural network framework that learns from actual operating data to model plant performance and accurately predict the PUE. The results demonstrated that machine learning is an effective way of leveraging existing sensor data to model DC performance and improve energy efficiency.

Figure 4: Taxonomy of power/energy optimization techniques in computer system.

- *Circuit design* : the work by Beloglazov et al. [13] presents Static Power Management (SPM) techniques that contains all optimization methods applied at the design time at various levels including *circuit, logic, architecture* and *system*. Circuit level optimizations consist in the reduction of switching in logic-gates and combination circuits through a complex gate design and transistor sizing.

- Energy-aware dedicated architectures: This category is for hardware level methods, which consider incorporating power optimization in the design process [13]. In other words, an efficient mapping of high-level specifications into the design of the chip is applied. Apart energy-aware hardware design, it is important to carefully consider a skillful programming that efficiently take into account the energy specificities of the target system. Most often, dedicated architectures (GPU, FPGA, TPU, etc.) are used for specific kernels based on the aforementioned observations.